# Design and Characterization of SEU Hardened Circuits for SRAM-Based FPGA

Tianwen Li<sup>®</sup>, Hongjin Liu, and Haigang Yang

Abstract—The mitigation of single-event upset (SEU) in SRAM-based field-programmable gate array (FPGA) is increasingly important as utilization and demand for SRAM-based FPGA dramatically increased in radiation environments such as space. As D flip-flop (DFF) and memory [including block random-access memory (BRAM) and configuration randomaccess memory (CRAM)] are constituted as the key elements in an FPGA, it is fundamentally necessary to develop radiation hardening techniques targeted for enhanced reliability of DFF and memory. A novel SEU hardened memory design for FPGA is proposed with capabilities of multibit upset protection. We further developed two prototype FPGA chips, one with SEU and the other without SEU hardening for comparison. The FPGA chips are fabricated in a standard 0.13-µm CMOS process and have a volume of three million equivalent logic gates. In terms of SEU cross section, CRAM in the hardened FPGA design is about four orders of magnitude lower than in the unhardened FPGA design, while BRAM demonstrates a reduction by three orders of magnitude. On the conditions of linear energy transfer being up to 14 MeV·cm<sup>2</sup>/mg, no SEU errors were observed from DFF in the hardened FPGA design.

Index Terms—Error correction code (ECC), memory, multibit upset (MBU), radiation hardened by design, single-event upset (SEU), SRAM-based field-programmable gate array (FPGA), triple interlocked latch (TILL).

# I. INTRODUCTION

S A circuit function of SRAM-based field-programmable gate arrays (FPGAs) is mainly defined by the content of the configuration memory [e.g., configuration random-access memory (CRAM)], they are considered as more vulnerable to single-event upsets (SEUs) than application-specific integrated circuit (ASIC) devices, where all the logic functions and interconnections are determined. With continued scaling of the integrated circuit feature size, the node capacitance and the supply voltage decrease altogether. Hence, the amount of charges stored on a node capacitor to hold a certain logic state are getting less, more prone to influences from cosmic ray,

Manuscript received August 5, 2018; revised December 11, 2018; accepted January 7, 2019. This work was supported by the National Science and Technology Major Project of China under Grant 2013ZX03006004. (Corresponding author: Hongjin Liu.)

- T. Li is with Beijing SunWise Space Technology Ltd., Beijing 100190, China (e-mail: litianwen@mail.ie.ac.cn).

- H. Liu is with the Beijing Institute of Control Engineering, Beijing 100190, China, and also with Beijing SunWise Space Technology Ltd., Beijing 100190, China (e-mail: lhjbuaa@163.com).

- H. Yang is with the Institute of Electronics, Chinese Academy of Sciences, Beijing 100190, China.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2019.2892838

or  $\alpha$ -particles originated by the decay of uranium and thorium impurities presented within packages [1]–[3], [17], [18]. These energetic particles will ionize a mass of electron-hole pairs in the semiconductor substrate, which may be collected by source/drain diffusions and hence possibly alter the existing logic state dedicated to a storage cell. This phenomenon is so-called SEU. When SEUs occur in whichever of the CRAM, the block random-access memory (BRAM), or the D flipflop (DFF) presented in an FPGA [19]-[21], the implemented functional design is impaired for its original behavior. SEU has long been known as a cumbersome problem for SRAMs because of their dense geometries organized in a highly compact fashion [4], [5]. Specifically, in those high reliability required applications such as space missions, military equipments, and avionics systems, an SEU impacted FPGA could result in a catastrophic operation failure.

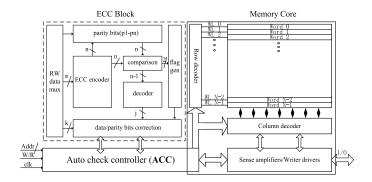

The issue of making SRAM-based FPGAs resilient to SEUs has been tackled mainly in two ways. One avenue of endeavors is to build some sort of redundancy in circuit implementations. Triple modular redundancy (TMR) with majority voters is commonly used to mask errors, combined with dynamic reconfiguration [8]. Unfortunately, the TMR is usually realized at a high cost in terms of area, speed, and power consumption. The other avenue of endeavors is to have an FPGA intrinsically designed with the SEU hardened storage element and circuitry. Toward this end, some intensive studies have been devoted to SEU hardened design of the memory, and the DFF being fit into FPGA. The DFF hardening methods can also be classified into two categories [6]. The first is to design a hardened DFF based on a special state locking mechanism. The second is to design a hardened DFF by enlarging node capacitance and driving strength. One example of the first category is the dual interlocked cell element (DICE) cell [7], which tolerates SEU without increasing the transistor size and the node capacitance. Error correction code (ECC) is typically used for hardening the memory in FPGA to detect the soft errors and recover the corrupt state. In this paper, we combine the extended hamming coding technique with the physical bit location interleaved to enhance the memory reliability. Moreover, a so-called autochecking controller (ACC) is proposed to constantly scan and correct bit errors accumulated in CRAM and SRAM. For DFF, the triple interlocked latch (TILL) structure previously published in [9] is applied, proven to have a higher SEU threshold than the conventional DICE structure.

The rest of this paper is organized as follows. Section II analyzes the SEU sensitivity characteristics arising from the SRAM-based FPGA. Section III discusses a comprehensive

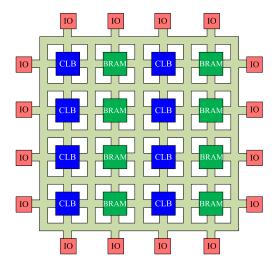

Fig. 1. Generic view of FPGA architecture.

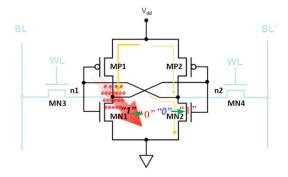

Fig. 2. Bit-flip occurrence in a memory cell.

design method proposed for SEU hardened FPGA. Section IV evaluates the effective performance of the proposed SEU hardened FPGA design. Irradiation test results are given in Section V. Finally, Section VI provides the conclusion.

# II. SEU SENSITIVITY ISSUES

A generic diagram of an FPGA is shown in Fig. 1, where clustered logic blocks (CLBs) and BRAMs are arranged in a 2-D grid and are interconnected by programmable routing channels. I/O blocks are arranged at the periphery of the grid, and they are also connected to the programmable routing interconnect.

An SRAM-based FPGA employs the static memory cells which are distributed throughout the entire chip to provide configurability. Example of such a memory cell is shown in Fig. 2. Those SRAM cells in FPGA are mainly served for the following purposes: 1) to program the routing interconnect which are generally steered by groups of the individual multiplexors and 2) to program CLBs that are used to implement logic functions.

Fig. 2 illustrates one bit memory cell impacted by an SEU, known as bit-flip. The circuit is desired to maintain state "1." For each state, a pair of p-n transistors is activated while the other pair of p-n transistors should be put OFF. A bit-flip happens when an energetic particle provokes the inversion of the cell state. The similar effect could also happen to a DFF.

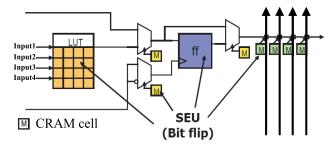

Fig. 3. SEU sensitivity due to CRAM cells.

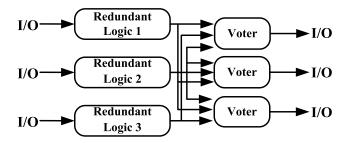

Fig. 4. TMR implementation architecture [8].

In FPGA, an upset in CRAM will impact the combinational or sequential logic circuits mapped onto the programmable architecture. Typically, compared with antifuse- and flash-based FPGA, SRAM-based FPGA can be quickly programed by loading a configuration bitstream (a series of binary codes) into the device. Such a bitstream is normally partitioned in frames and contains all the information necessary to configure the CRAM cells located around the look-up tables (LUTs), flip-flops, CLB control circuits, and interconnections, as shown in Fig. 3. All these configuration bits are extremely sensitive to SEU.

# III. FPGA HARDENING TECHNIQUES

As mentioned earlier, there are generally two ways to reduce the SEU sensitivity for SRAM-based FPGA, i.e., TMR or embedding SEU hardened data storage elements. Those two approaches will be discussed in the following.

## A. TMR-Based Techniques

The basic concept of the TMR implementation architecture is to have three identical circuits designed with a majority voter that makes decisions on the three output results. In the case of ASIC, TMR just needs to be applied to the embedded memory, exclusive of those determined logic functions, and interconnections. However, in the case of FPGA, TMR is required for all the CRAM cells besides the embedded memories, since all the logic functions, interconnections, and I/O interfaces are programed by CRAMs. Thus, a large amount of area overheads will be taken [8], as illustrated in Fig. 4.

#### B. SEU Hardened Elements

The SEU sensitivity of SRAM-based FPGA is essentially decided by DFF and memory (both CRAM and BRAM). Apparently, when those elements are replaced by

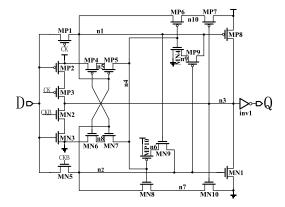

Fig. 5. TILL circuit proposed in [9].

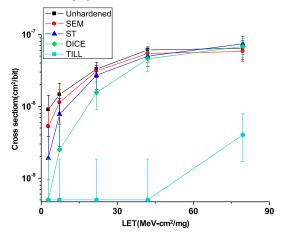

Fig. 6. SEU CS for each type of the latch tested in [9].

SEU hardened designs, the FPGA reliability shall be greatly improved.

1) SEU Hardened DFF: There are two aspects that should be considered in strengthening latch design for even higher SEU tolerant capability. Apart from employing additional locking loops to restore the original state for a transient fault (TF) impacted node, reducing the number of sensitive node pairs (i.e., a single or more particles strike at the latch and cause TFs to simultaneously happen at two nodes (hence corrupting a correct stored state) should be further beneficial.

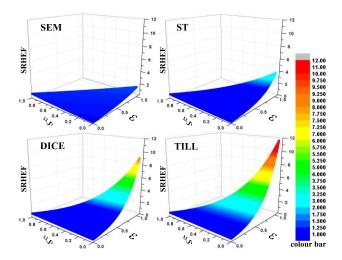

As shown in Figs. 5 and 6, from four SEU hardened forms, namely, soft error masking, Schmidt trigger, DICE, and TILL proposed in [9], TILL has achieved its SEU threshold of above 42 MeV  $\cdot$  cm<sup>2</sup>/mg, the highest among the compared designs. SEU radiation hardening efficiency factor (SRHEF) is a metric to take into account the overall performance evaluation for a latch, not only on radiation hardening effect but also on the area and power-delay product (PDP). SRHEF can be used as a guideline for design optimization. Assume that  $\varepsilon$ ,  $\xi$ , and  $\gamma$  represent the normalized weight factors for SER, area, and PDP, respectively,

$$\varepsilon + \xi + \gamma = 1. \tag{3.1}$$

Then, we have

$$SRHEF = \frac{(SER_{Un}/SER)^{\varepsilon}}{(Area/Area_{Un})^{\xi} \times (PDP/PDP_{Un})^{\gamma}}$$

(3.2)

Fig. 7. SEU radiation hardening efficiency factor for each latch analyzed in [9].

where SER<sub>Un</sub>, Area<sub>Un</sub>, and PDP<sub>Un</sub> correspond to the unhardened latch. As the unhardened latch is regarded as a reference design, SRHEF of the unhardened latch should always be 1.

TILL has higher SRHE than the previously hardened latches as shown in Fig. 7. There are about 35 840 DFFs in our FPGA. When all the conventional DFFs were replaced by the TILL DFFs, the area merely increases by about 0.31% in our FPGA design.

2) SEU Hardened Memory: In order to mitigate the soft errors occurred in CRAMs and BRAMS of FPGA, a systematical approach is attempted at both the circuit and the architectural level for the combined effect of improved SEU hardening performance. Several coding schemes for singleerror correction (SEC) or double-adjacent error correction have recently been proposed to tackle the SEU problem in memories [10]–[13]. A more robust coding design is presented in [14], combining both double error and burst error correction capabilities for a data word of up to 24 bits, but at a high cost in redundancy. Regarding CRAM or BRAM in FPGA, the SEC coding may be preferable due to its lower area overhead. Hence, the SEC and double error detection (SEC-DED) coding are used. In a way, the SEC-DED coding requires storing seven check bits for a 32-bit data, increasing the memory array size approximately just by 22%. This is compared to the case where the DICE storage cell is implemented, resulting in the memory array size being increased by 100%.

As shown in Fig. 8, the memory structure (either CRAM or BRAM) mainly consists of three parts, namely, memory core, ECC block, and ACC. The process where the data are written to or read from the SRAM array is through the memory core. The ECC block encodes the input data from I/O when in write process and decodes the data from the memory core when in read process. The ACC block is used to examine the content readback from the SRAM cells and further to correct the error bits by writing into the SRAM cells with the recovered code. Such a "identify and repair" operation is carried out in background without any interruptions to the functionality of the whole device. ACC will look through each

Fig. 8. Architecture diagram of SEU hardened memory.

Fig. 9. Fundamental of bit location interleaving in memory.

row of the memory at frequency "clk." Accordingly, failure in ACC becomes then critical for FPGA, TILL has been used to enhance the SEU tolerant capability of ACC.

According to the reliability model for SEC/DED memories with "identify and repair" operation [16], the mean time to failure for embedded FPGA memories can be calculated in the following equation:

$$MTTF = \frac{2 \times \nu}{M \times \lambda^2 \times N \times (N-1)}$$

(3.3)

where  $\nu$  is the correction rate,  $\lambda$  is the bit failure rate, N is the number of bits in a single word, and M is the number of words in the memory. Thus, MTTF is proportional to ACC frequency.

In order to achieve multibit upset (MBU) mitigations with minimum area overhead of the added-in circuit, the combination measures are taken, as listed below.

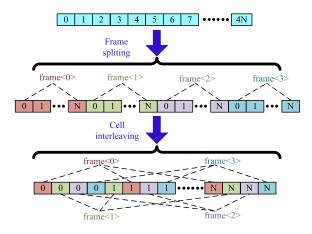

- a) Scattered locations of the bit cells in the same frame for nonadjacency: The configuration data stream can be split into some smaller frames, and all the bit cells of a frame are scattered over a distance. In [14], a minimum interleaving distance of four to eight is recommended for 150-nm SRAMs. It should, therefore, be larger than four for 130-nm SRAM, say, of 7 bits as shown in Fig. 9 to prevent MBU from happening to the same frame.

- b) Built-In single-bit error correction and double-bit error detection: Thus, for scattered cells of a frame, an extended Hamming coding scheme is sufficiently applied

Fig. 10. (a) Layout of the base FPGA design (area = 1.92 cm  $\times$  2.04 cm). (b) Layout of the SEU hardened FPGA design (area = 1.98 cm  $\times$  2.08 cm).

Fig. 11. (a) Layout of the base BRAM design (area =  $580~\mu m \times 300~\mu m$ ). (b) Layout of the SEU hardened BRAM design (area =  $646~\mu m \times 300~\mu m$ ).

to correct any single bit error and detect possible double bit errors.

c) Self-Checking: ACC is designed to run in the background and without any disturbance to normal executions of the circuit function. If an error is detected in a configuration frame or in a memory word, it shall be immediately remedied. For the self-checking operation, CRAM is designed to support the four levels of the running frequency, giving some balanced choices between the SEU hardening performance, and power consumption considerations. BRAM is designed to have the self-checking frequency to be decided by the user clock.

# IV. EVALUATION

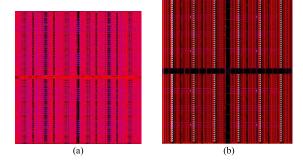

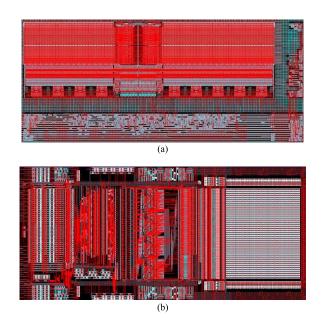

The layout diagrams, respectively, for the base FPGA (without hardening measures included) and for the hardened FPGA designs are shown in Fig. 10. The area overhead arising from added circuitry is estimated as 20.16 mm<sup>2</sup>, an increase of merely 5.15%. To further characterize, the layout diagrams, respectively, for the base BRAM design and for the hardened BRAM design are also given in Fig. 11. Floorplan optimization of hardened BRAM has been made to keep shape and data

TABLE I RESOURCE OF THE FPGA

| Logic |       | I/O      |      | MEMORY    |        |

|-------|-------|----------|------|-----------|--------|

| LUT   | DFF   | USER I/O | LVDS | BRAM      | CRAM   |

| 35840 | 35840 | 512      | 256  | 1728Kbits | 4Mbits |

$\label{eq:table_ii} \textbf{ACC}_{\textbf{CRAM}} \ \textbf{Can Work at Four Levels of the Frequency}$

| Frequency(MHz)              | 60.00  | 7.50  | 0.47 | 0.06 |

|-----------------------------|--------|-------|------|------|

| Increased FPGA current (mA) | 38.6   | 2.9   | 0.8  | 0.5  |

| Increased by percent        | 193.0% | 14.5% | 4.0% | 2.5% |

flow consistency. It can be seen that adding of the ACC and the ECC circuitry leads to increasing of the area by 11.42%. In a similar way, the layout area for the CRAM array is also increased for adding the ACC and the ECC circuitries and it is about 3.8%. The test chips for the base FPGA and the SEU hardened FPGA designs have been fabricated on a commercial  $0.13-\mu m$  bulk CMOS process. Both FPGA designs contain the same programmable resource, 35 840 LUTs, 512 I/Os, 1728-kbits BRAM, and 4-Mbits CRAM in both FPGAs, as shown in Table I.

They were tested at a supply voltage of 1.5 V and at room temperature. The static current of both FPGAs is about 20 mA, and the increased current consumption of the SEU hardened CRAM at different ACC<sub>CRAM</sub> frequencies is shown in Table II. Taking power consumption and circuit limitations into account, four levels of frequency are designed in ACC<sub>CRAM</sub>. If the user clock is 10 MHz, ACC<sub>BRAM</sub> would work at the same frequency, and the increased supply current is 1.5 mA for all BRAMs in FPGA. According to the radiation test results, when ACC circuit works at high frequency, the current would increase accordingly. Also, the SEU tolerant capability is hence greatly improved. Consequently, there should be a compromise between reliability and power consumption.

# V. RADIATION EXPERIMENT

Before the radiation tests, the relationship between ACC frequency and flux rate of ion beam had been evaluated to guide the radiation experiment. With fixed ACC frequency, the decreasing of ion flux rate may lead to the decreasing of upsets in the memory. Maximum ion flux rate could be calculated by the evaluation model given in Section V-A. Then, the irradiation environment and test results will be illustrated and analyzed.

#### A. ACC-Frequency Estimation

As a rule of thumb, the speed for scanning and refreshing the entire CRAM and BRAM arrays should be ten times higher than the flux rate of ions, allowing sufficient time for a bit-flip error to be corrected before the next possible SEU. For around four million CRAM cells and two million BRAM cells existing in our FPGA design, it typically requires about one second to accomplish a checking and correction run at 60 and 10 MHz, respectively. Concerning the radiation process, the flux indicates heavy ions incident in waves into the chip. For convenience of calculation, we assume that the total influx of irons is equally divided and modeled in two consecutive waves.

At the time of impacting by the first wave, the CRAM and BRAM arrays are going through the checking phase. Then, at the next time of impacting by the second wave, the CRAM and BRAM arrays are going through the correction phase. Note that both CRAM and BRAM could correct one bit error in a word. Suppose the flux rate of irons F is taken in ions/( $\mu$ m<sup>2</sup> × 0.5 S). In order to find the maximum flux rate of irons at which any bit-flip error can be recovered, the following equations are derived:

$$M_{\text{upsets}} = F \times 0.5 \times T \times A_{\text{SRAM}}$$

(5.1)

$$A_{\text{affacted}} = M_{\text{upsets}} \times (W_{\text{word}} - 1) \times A_{\text{SRAM}}$$

(5.2)

$$N_{\text{upsets}} = F \times 0.5 \times A_{\text{affacted}} < \text{one upset}$$

(5.3)

$$F^2 \times 0.25 \times A_{\text{SRAM}}^2 \times (W_{\text{word}} - 1) \times T < \text{one upset}$$

(5.4)

$$F < \frac{1}{0.5 \times A_{\text{SRAM}} \times \sqrt{(W_{\text{word}} - 1) \times T}}.$$

(5.5)

$A_{\rm SRAM}$  denotes the area of the SRAM cell, T denotes the total number of the SRAM cells, and  $W_{\rm word}$  denotes the word width.  $M_{\rm upset}$  is the upset number in first wave (5.1), and  $A_{\rm affacted}$  is the area SRAM that is affected by  $M_{\rm upset}$  (5.2). If another ion is falling into this area in the same  $W_{\rm word}$ , which already has an error, ACC cannot deal with it in this case. So, the upset number  $N_{\rm upset}$  in second wave should be no more than 1 (5.4). The maximum flux rate is given in (5.5).

After calculation, the ion flux rate  $F_{\text{CRAM}}$  for the CRAM array must be less than 416 ions/(cm<sup>2</sup> · S), while the ion flux rate  $F_{\text{BRAM}}$  for BRAM must be less than 5945 ions/(cm<sup>2</sup> · S). The above-mentioned model is based on the assumptions listed as follows.

- The incident irons are uniformly distributed across the whole chip.

- 2) Each ion stands for the same chance to cause an upset.

- 3) Upsets happening to any pair of the cells within a single word would not occur during the impact by a single wave of ions.

## B. Radiation Test

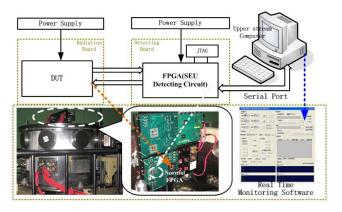

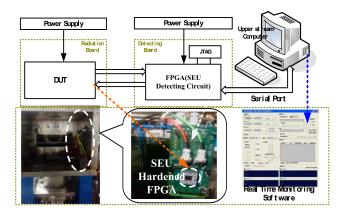

The test chips for both the base FPGA and the hardened FPGA were designed to determine the effectiveness of the SEU hardening measures mentioned above. Furthermore, those FPGA designs were tested at the China Institute of Atomic Energy (CIAE) and the Institute of Heavy Ion Physics of Peking University, Beijing, China, respectively. The irradiation environment and test setup are illustrated in Figs. 12 and 13.

The onsite test system is mainly made up of three parts: the test chip, an SEU detecting board, and an upper stream computer. The storage data from DFF, BRAM, and CRAM were sent in and readback by a commercial FPGA device

Fig. 12. SEU detecting system and irradiation environment or the base FPGA design at CIAE.

Fig. 13. SEU detecting system and irradiation environment for the SEU hardened FPGA design at Peking University.

$\begin{tabular}{ll} TABLE III \\ Characteristics of Ion Beams Used at CIAE \\ \end{tabular}$

| Ion                           | С    | О   | Ti   |  |

|-------------------------------|------|-----|------|--|

| Energy (MeV)                  | 79   | 100 | 180  |  |

| LET (MeV-cm <sup>2</sup> /mg) | 1.63 | 3.1 | 21.8 |  |

| Range in target (µm)          | 14   | 11  | 34.7 |  |

| Flux(ions/cm <sup>2</sup> *S) | 5000 |     |      |  |

| Fluence(ions) 1E+7            |      |     |      |  |

on the detecting board. When a mismatch is detected, the data are stored and at intervals transported via a cable to the serial port of the upper stream computer for analysis. The test chips together with the SEU detecting boards were placed in the vacuum chamber to minimize the energy loss of incident ions. Three types of heavy ions (e.g., C, F, and Ti) were used in the experiment for the base FPGA design, when the irons C, F, and Si were chosen for test of the SEU hardened FPGA design. Under the irradiation, each chain of memory cells was tested with three different linear energy transfer (LET) levels. The energy, range in target, LET, flux, and fluence of those ions used are listed in Tables III and IV. The chips were tested at a supply voltage of 1.5 V. The

TABLE IV

CHARACTERISTICS OF ION BEAMS USED AT PEKING UNIVERSITY

| Ion                            | С    | F    | Si    |

|--------------------------------|------|------|-------|

| Energy (MeV)                   | 25   | 35   | 40    |

| LET (MeV-cm <sup>2</sup> /mg)  | 3.53 | 6.78 | 13.65 |

| Range in target (µm)           | 25.7 | 21   | 14.2  |

| Flux (ions/cm <sup>2</sup> *S) | 500  |      | •     |

| Fluence (ions)                 | 1E+6 |      |       |

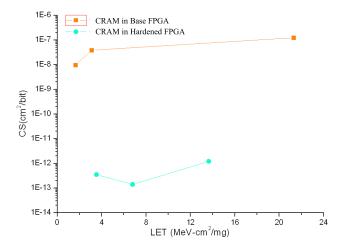

Fig. 14. SEU CS of CRAM.

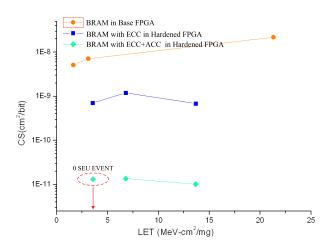

Fig. 15. SEU CS of BRAM.

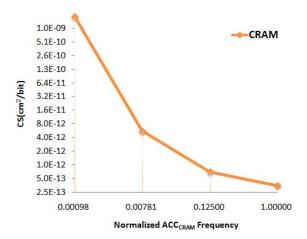

ACC operations of CRAM and BRAM in the hardened FPGA design are clocked at 60 and 10 MHz, respectively. The measured SEU cross sections (CSs) of CRAM are given in Fig. 14. It can be seen that, at LET from 3.53 to 13.65 MeV · cm²/mg, the SEU CS of the hardened CRAM was about 1E-12 cm²/bit, which is at least two orders of magnitude lower compared to the base CRAM. Radiation test results for BRAMs are given in Fig. 15. When only ECC was enabled in the hardened BRAM, its SEU CS was 1 order of magnitude lower than the base BRAM. Especially, when ECC and ACC were both

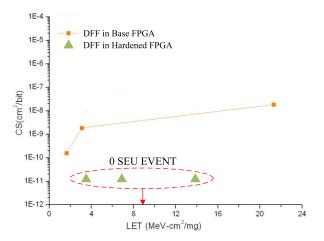

Fig. 16. SEU CS of DFF.

enabled, there was no upset observed under the irradiation by iron C, and the SEU CS of the hardened design is reduced to 1E–11 cm<sup>2</sup>/bit, about three orders of magnitude lower compared to the base BRAM. Apparently, at LET from 3.53 to 13.65 MeV · cm<sup>2</sup>/mg, there was no SEU happened to the DFFs in the SEU hardened FPGA, as shown in Fig. 16. This is owing to the sufficiently high-LET threshold of the TILL structure used in the design, which is consistency with the observation in [9].

When the ion strikes at a shallow angle, it is expected that the SEU CSs of both the base FPGA and the hardened FPGA gets worse. However, as there is lower percentage of the sensitive node pairs existing in the TILL than in unhardened DFF, superiority of the TILL in terms of the SEU CS should still be valid in the circumstances just mentioned. Similarly, the bit interleaving techniques used in the CRAM and the BRAM designs could also mitigate MBU sufficiently when the ion strikes at a shallow angle. According to (5.5), if the flux is below 416 ions/(cm<sup>2</sup>·S), both CRAM and BRAM could efficiently correct the bit error. As shown in Figs. 14 and 15, with LET ranging from 3.53 to 13.65 MeV · cm<sup>2</sup>/mg, few upsets happen in both the BRAM and the CRAM memories. Fig. 17 shows as expected that if the flux rate of ion C is 500 ions/(cm<sup>2</sup>·S), SEU CS of CRAM is significantly reduced with the increase of ACC<sub>CRAM</sub> frequency. More single errors in a word can be corrected at higher ACC frequency as the number of accumulated errors is reduced.

# C. Comparison

Comparison between the existing commercial radiation hardened FPGA devices and proposed design will be made in this section. The susceptibility of the previous SEU hardened FPGAs, such as UltraScale, which is Xilinx's first product offering built using TSMC's 20-nm, 20-SoC process, had been previously tested for the purpose of estimating terrestrial upset rates [22]–[26], the radiation test results for Virtex II, Virtex-4, Kintex-7, and Ultrascale are given in Table V. In the same LET range, radiation test results of CRAM, BRAM, and DFF are concluded in Table V. Obviously, the SEU tolerant capacity of the proposed FPGA is better than the previous designs,

Fig. 17. SEU CS of the CRAM in the hardened FPGA design obtained at different ACC frequencies and with C ion flux rate of  $500 \text{ ions/(cm}^2 \cdot \text{S)}$ .

TABLE V

SEU TOLERANT CAPABILITY FOR DIFFERENT HARDENED FPGAS

| Туре                                           | Virtex II | Virtex-4 | Kintex-7 | Ultrascale | Proposed |

|------------------------------------------------|-----------|----------|----------|------------|----------|

| Node                                           | 130nm     | 90nm     | 28nm     | 20nm       | 130nm    |

| CRAM<br>(cm²/bit)                              | 2E-8      | 8E-9     | 2E-9     | 8E-10      | 1E-12    |

| BRAM<br>(cm²/bit)                              | 5E-8      | 1E-8     | 8E-9     | 1.5E-9     | 1E-11    |

| DFF SEU threshold<br>(MeV-cm <sup>2</sup> /mg) | <7        | <7       | <7       | <7         | >42      |

which is mainly due to the two following facts: 1) larger device feature size effect, which means when the same charge cloud caused by energetic ions, fewer storage cells may be affected, and 2) combinational measures are used to enhance the SEU tolerant capability of the proposed FPGA, which could dramatically reduce its upset CSs.

# VI. CONCLUSION

In this paper, we propose an SEU hardened FPGA design involving high reliability storage cells and error correction mechanism. In comparison to the base (unhardened) FPGA, the area of the hardened FPGA increases just about 5.15%. An ACC<sub>CRAM</sub> is implemented in the hardened FPGA for background error correction, and it supports four levels of the checking frequency all generated on chip. The frequency of ACC<sub>BRAM</sub> is determined by the user clock. According to the irradiation experimental results, when ACC<sub>CRAM</sub> is clocked at 60 MHz, the SEU CS of the hardened CRAM is at least four orders of magnitude lower compared to the base CRAM. Accordingly, when ACC<sub>BRAM</sub> is clocked at 10 MHz, the SEU CS of the hardened BRAM is about three orders of magnitude lower compared to the base BRAM. Moreover, at LET level of 3.53–13.65 MeV · cm<sup>2</sup>/mg, there was no SEU occurring to the DFFs in the hardened FPGA design. Moreover, compared with the previous hardened FPGAs, proposed FPGA exhibits better SEU tolerant capability, which takes the advantage of technology node and multiple hardening measures.

#### ACKNOWLEDGMENT

The authors would like to thank Z. Qi, Dr. Y. Luo, C. Xu, and Y. Li for their suggestions in designing the single-event upset detecting system. They would like to thank Prof. G. Guo and his group at the China Institute of Atomic Energy, Beijing, China. They would also like to thank Prof. X. Ren and his group at Peking University, Beijing, for their assistance in the irradiation experiment.

#### REFERENCES

- G. C. Messenger, "Collection of charge on junction nodes from ion tracks," *IEEE Trans. Nucl. Sci.*, vol. NS-29, no. 6, pp. 2024–2031, Dec. 1982.

- [2] S. Kang and D. Chu, "CMOS circuit design for the prevention of single event upset," in *Proc. IEEE Int. Conf. Comput. Design*, Oct. 1986, pp. 385–388.

- [3] O. A. Amusan *et al.*, "Mitigation techniques for single-event-induced charge sharing in a 90-nm bulk CMOS process," *IEEE Trans. Device Mater. Rel.*, vol. 9, no. 2, pp. 311–317, Jun. 2009.

- [4] A. B. Boruzdina et al., "Temperature dependence of MCU sensitivity in 65 nm CMOS SRAM," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 6, pp. 2860–2866, Dec. 2015.

- [5] M. S. Gorbunov et al., "Design of 65 nm CMOS SRAM for space applications: A comparative study," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 4, pp. 1575–1582, Aug. 2014.

- [6] M. Nicolaidis, R. Perez, and D. Alexandrescu, "Low-cost highly-robust hardened cells using blocking feedback transistors," in *Proc. IEEE VLSI Test Symp.*, Apr./May 2008, pp. 371–376.

- [7] T. Calin, M. Nicolaidis, and R. Velazco, "Upset hardened memory design for submicron CMOS technology," *IEEE Trans. Nucl. Sci.*, vol. 43, no. 6, pp. 2874–2878, Dec. 1996.

- [8] C. Carmichael, Triple module redundancy design techniques for Virtex FPGAs. Xilinx, San Jose, CA, USA, Appl. Note XAPP197, Jul. 2006.

- [9] T. Li, H. Yang, G. Cai, T. Zhi, and Y. Li, "A CMOS triple inter-locked latch for SEU insensitivity design," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 3265–3273, Dec. 2014.

- [10] A. Dutta and N. A. Touba, "Multiple bit upset tolerant memory using a selective cycle avoidance based SEC-DED-DAEC code," in *Proc. IEEE VLSI Test Symp.*, May 2007, pp. 349–354.

- [11] A. Neale and M. Sachdev, "A new SEC-DED error correction code subclass for adjacent MBU tolerance in embedded memory," *IEEE Trans. Device Mater. Rel.*, vol. 13, no. 1, pp. 223–230, Mar. 2013.

- [12] S. Baeg, S. Wen, and R. Wong, "SRAM interleaving distance selection with a soft error failure model," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 4, pp. 2111–2118, Aug. 2009.

- [13] A. Dutta, "Low cost adjacent double error correcting code with complete elimination of miscorrection within a dispersion window for multiple bit upset tolerant memory," in *Proc. IEEE/IFIP 20th Int. Conf. VLSI Syst.-Chip*, Oct. 2012, pp. 287–290.

- [14] S. Shamshiri and K.-T. Cheng, "Error-locality-aware linear coding to correct multi-bit upsets in SRAMs," in *Proc. IEEE Int. Test Conf.*, Nov. 2010, pp. 1–10.

- [15] S. Lee, S. H. Jeon, S. Baeg, and D. Lee, "Memory reliability analysis for multiple block effect of soft errors," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 2, pp. 1384–1389, Apr. 2013.

- [16] Y. Li, B. Nelson, and M. Wirthlin, "Reliability models for SEC/DED memory with scrubbing in FPGA-based designs," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 4, pp. 2720–2727, Aug. 2013.

- [17] D. Hiemstra, V. Kirischian, and J. Brelski, "Single event upset characterization of the Zynq UltraScale+ MPSoC using proton irradiation," in *Proc. Radiat. Effects Data Workshop (REDW)*, 2017, pp. 1–4.

- [18] P. Maillard, M. Hart, J. Barton, P. Jain, and J. Karp, "Neutron, 64 MeV proton, thermal neutron and alpha single-event upset characterization of Xilinx 20nm UltraScale Kintex FPGA," in *Proc. Radiat. Effects Data Workshop (REDW)*, 2015, pp. 1–5.

- [19] C. Bernardeschi, L. Cassano, A. Domenici, and L. Sterpone, "Unexcitability analysis of SEus affecting the routing structure of SRAM-based FPGAs," in *Proc. ACM Int. Conf. Great Lakes Symp. VLSI*, 2013, pp. 7–12.

- [20] C. Bernardeschi, L. Cassano, M. G. C. A. Cimino, and A. Domenici, "Application of a genetic algorithm for testing SEUs in SRAM-FPGA Systems," in *Proc. 6th HiPEAC Workshop Reconfigurable Comput.* (WRC2012), 2012, pp. 1–10.

- [21] S. Di Carlo, S. Prinetto, D. Rolfo, and P. Trotta, "A fault injection methodology and infrastructure for fast single event upsets emulation on Xilinx SRAM-based FPGAs," in *Proc. IEEE Int. Symp. Defect Fault Tolerance VLSI Nanotechnol. Syst.* Washington, D.C., USA: IEEE Computer Society, Oct. 2014, pp. 159–164.

- [22] D. S. Lee et al., "Single-event characterization of the 20 nm Xilinx Kintex Ultrascale field-programmable gate array under heavy ion irradiation," in Proc. IEEE Radiat. Effects Data Workshop (REDW), Jul. 2015, pp. 1–6.

- [23] D. Berg et al, "Independent single event upset testing of the Xilinx V5QV," in Proc. Single Event Effects (SEE) Symp. Mil. Aerosp. Program. Logic Devices Workshop (MAPLD), La Jolla, CA, USA, May 2014.

- [24] G. Allen, G. Swift, and C. Carmichael, "VIRTEX-4 VQ static SEU characterization summary," Jet Propuls. Lab., Pasadena, CA, USA, NASA Tech. Rep. 08–16, 2008.

- [25] C. Carmichael, E. Fuller, P. Blain, and M. Caffrey, "SEU mitigation techniques for Virtex FPGAs in space applications," in *Proc. Mil. Aerosp. Program. Logic Devices Int. Conf. (MAPLD)*, 1999, p. C2.

- [26] D. S. Lee, M. Wirthlin, G. Swift, and A. C. Le, "Single-event characterization of the 28 nm Xilinx Kintex-7 field-programmable gate array under heavy ion irradiation," in *Proc. IEEE Radiat. Effects Data Workshop (REDW)*, Jul. 2014, pp. 1–5.

**Tianwen Li** received the B.S. degree in physics from the University of Science and Technology Beijing, Beijing, China, in 2010, and the Ph.D. degree from the University of Chinese Academy of Sciences, Beijing, in 2015.

He is currently with Beijing SunWise Space Technology Ltd., Beijing, China. His current research interests include high-performance integrated circuit design and radiation hardened by design.

**Hongjin Liu** received the B.S. degrees from Beihang University, Beijing, China, in 2003, and the Ph.D. degree from the Graduated University of Chinese Academy of Sciences, Beijing, in 2008.

He is currently a Professor and the Director of the IC Department, Beijing Institute of Control Engineering and Beijing SunWise Space Technology Ltd., Beijing. His current research interests include on-board computer design, integrated electronic system design of satellite, and SoC- and SiP-based microelectro systems.

**Haigang Yang** received the B.Sc. and M.Sc. degrees from Fudan University, Shanghai, China, in 1983 and 1986, respectively, and the Ph.D. degree from the University of Cambridge, Cambridge, U.K., in 1991.

He was with Wolfson Microelectronics, Edinburgh, U.K., LSI Logic Europe, Bracknell, U.K., and Altera Europe, Bracknell. He is currently a Professor with the System on Programmable Chip Research Department, Institute of Electronics, Chinese Academy of Sciences, Beijing, China.

His current research interests include VLSI design, high-reliability field-programmable gate array device.